How to Get Counter to Start at 0 Again

What is a Counter?

A counter is a device which can count any particular event on the basis of how many times the particular issue(south) is occurred. In a digital logic system or computers, this counter tin can count and shop the number of fourth dimension any particular effect or process accept occurred, depending on a clock signal. About common type of counter is sequential digital logic circuit with a unmarried clock input and multiple outputs. The outputs represent binary or binary coded decimal numbers. Each clock pulse either increase the number or decrease the number.

Synchronous Counter

Synchrounous generally refers to something which is cordinated with others based on time. Synchronous signals occur at aforementioned clock charge per unit and all the clocks follow the same reference clock.

In previous tutorial of Asynchronous Counter, we have seen that the output of that counter is direct connected to the input of next subsequent counter and making a chain system, and due to this concatenation system propagation delay appears during counting stage and create counting delays. In synchronous counter, the clock input beyond all the flip-flops use the same source and create the aforementioned clock signal at the same time. So, a counter which is using the same clock signal from the aforementioned source at the same time is called Synchronous counter.

Synchronous Up Counter

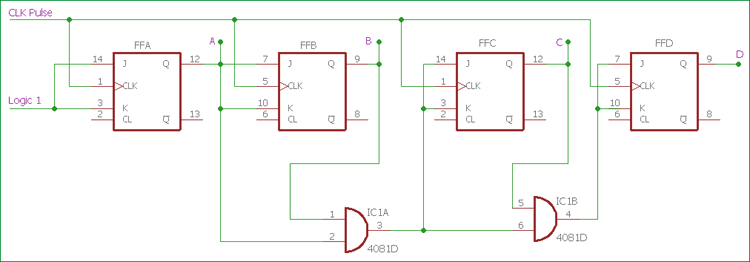

In the higher up image, the basic Synchronous counter blueprint is shown which is Synchronous up counter. A four-bit Synchronous up counter beginning to count from 0 (0000 in binary) and increment or count upwards to xv (1111 in binary) and then kickoff new counting cycle past getting reset. Its operating frequency is much higher than the aforementioned range Asynchronous counter. Also, at that place is no propagation delay in the synchronous counter only considering all flip-flops or counter phase is in parallel clock source and the clock triggers all counters at the same fourth dimension.

The external clock is directly provided to all J-Chiliad Flip-flops at the same fourth dimension in a parallel way. If nosotros run into the circuit, the beginning flip-flop, FFA which is the least pregnant bit in this 4-fleck synchronous counter, is connected to a Logic 1 external input via J and K pivot. Due to this connectedness, Loftier logic across the Logic ane signal, alter the land of showtime flip-bomb on every clock pulse.

Next phase, the 2nd flip-bomb FFB, input pin of J and One thousand is continued across the output of the first Flip-flop. For the example of FFC and FFD, two dissever AND gate provide the necessary logic across them. Those AND gates create logic using the input and output from the previous stage flip-flops.

Nosotros tin can create the same counting sequence used in the Asynchronous counter by making a situation where each flip-flops change its state depending on whether or not all preceding flip-flops output is HIGH in logic. Only in this scenario, there volition be no ripple effect just because all flip-flops are clocked at the same time.

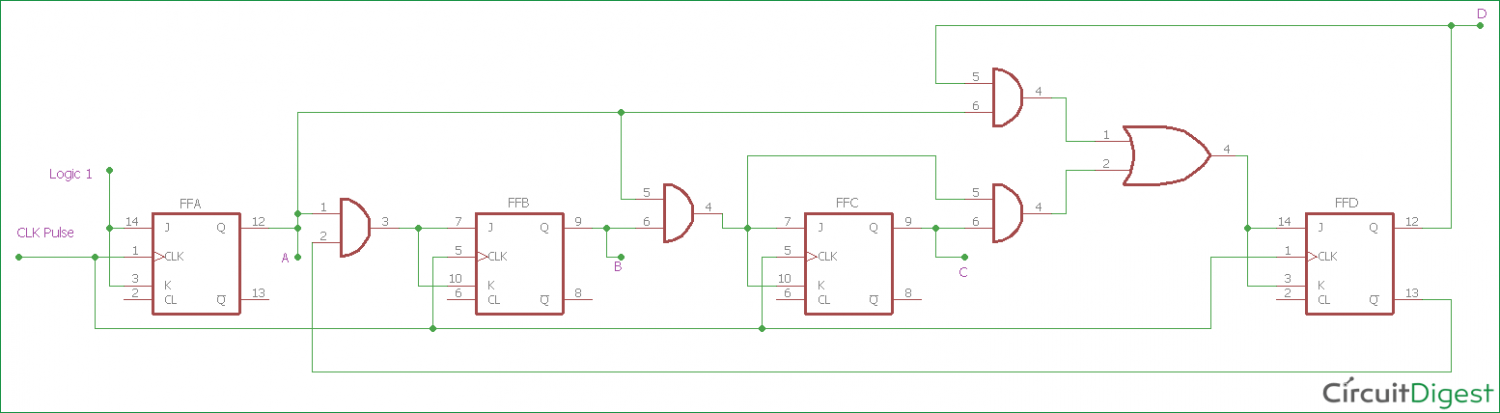

Synchronous Down Counter

Slight changes in AND section, and using the inverted output from J-G flip-flop, we tin can create Synchronous Downward Counter. A 4-bit Synchronous down counter start to count from 15 (1111 in binary) and decrement or count downwards to 0 or 0000 and after that it volition start a new counting bicycle by getting reset. In synchronous down counter, the AND Gate input is changed. First Flip-flop FFA input is same as nosotros used in previous Synchronous up counter. Instead of direct feeding the output of the offset flip-flop to the next subsequent flip-flop, we are using inverted output pin which is used to give J and Thousand input across side by side flip-flop FFB and also used every bit input pin across the AND gate. Aforementioned as like the previous excursion, two AND gates are providing necessary logic to the next ii Flip-flops FFC and FFD.

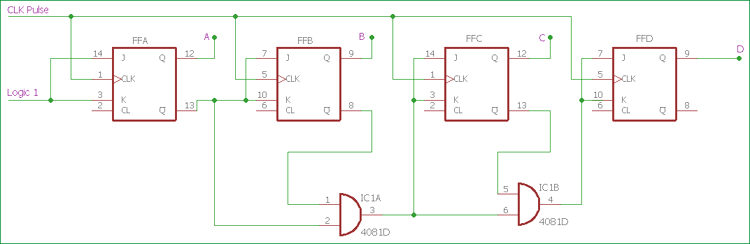

Synchronous Counter Timing Diagram

In the to a higher place image, clock input across flip-flops and the output timing diagram is shown. On each clock pulse, Synchronous counter counts sequentially. The counting output across four output pivot is incremental from 0 to xv, in binary 0000 to 1111 for 4-bit Synchronous up counter. Later the xv or 1111, the counter reset to 0 or 0000 and count once again with a new counting cycle.

For Synchronous down counter where the inverted output is connected across the AND gate, exactly opposite counting pace happens. The counter starts to count from 15 or 1111 to 0 or 0000 and so become restarted to starting time a new counting cycle and once more start from 15 or 0000.

4 fleck-Synchronous Decade Counter

Same equally similar Asynchronous counter, a Decade counter or BCD counter which can count 0 to can be made past cascading flip-flops. Same as like Asynchronous counter, it will also take "split up by northward" characteristic with modulo or Modern number. Nosotros demand to increase the MOD count of the Synchronous counter (can exist in Up or Downwardly configuration).

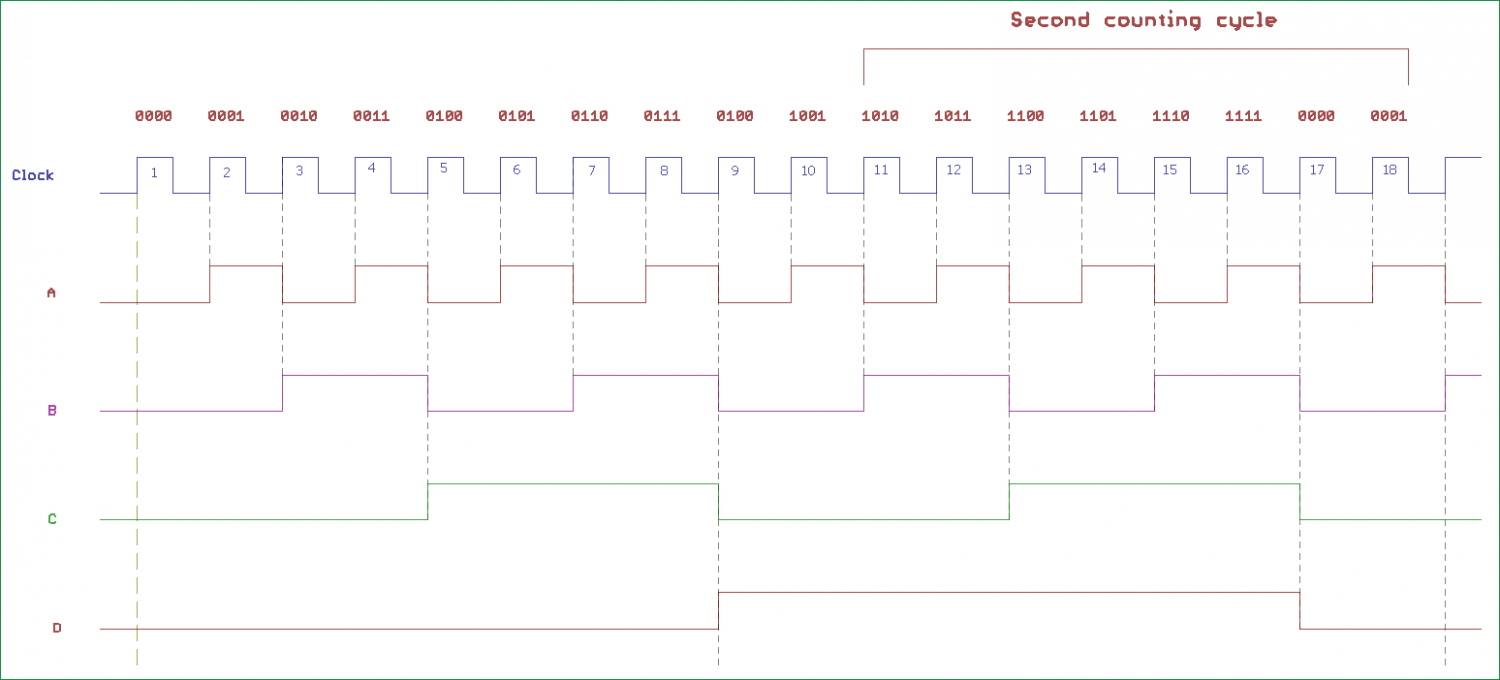

Hither is the iv-bit Synchronous Decade counter circuit is shown-

Above circuit is made using Synchronous binary counter, which produces count sequence from 0 to nine. Additional logics are implemented for desired land sequence and to convert this binary counter to decade counter (base ten numbers, Decimal). When the output reaches count 9 or 1001, the counter volition reset to 0000 and again counts up to 1001.

In the higher up circuit, AND gates volition discover the counting sequence reaches 9 or 1001 and change the state of a third flip-bomb from the left, FFC to change its state on the next clock pulse. The counter then resets to 000 and once more starts to count until 1001 is reached.

MOD-12 tin can be made from the above circuit if we change the position of AND gates and it volition count 12 states from 0 (0000 in binary) to eleven (1011 in binary) and and then reset to 0.

Trigger Pulse related data

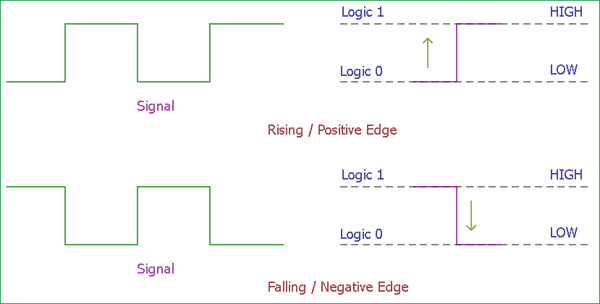

There are ii type of border triggered flip-flops available, Positive edge or Negative edge.

Positive Edge or Ascent Border flip-flops count one single footstep when the clock input changes its land from Logic 0 to Logic one, in other term Logic Depression to Logic Loftier.

On the other hand, Negative Edge or falling Edge flip-flops count one unmarried step when the clock input changes its country from Logic one to Logic 0, in other term Logic High to Logic Low.

Ripple counters utilise falling edge or negative border triggered clock pluses to change state. In that location is a reason behind it. Information technology will brand easier opportunities to pour counters together every bit the Most Significant bit of ane counter could drive the clock input of next counter.

Synchronous counter offering carry out and acquit in pin for counter linking related application. Due to this, at that place is no propagation filibuster inside the circuitry.

Advantages and Disadvantage of Synchronous Counter

Now we are familiar with Synchronous counter and what are the departure between the Asynchronous counter and Synchronous counter. Synchronous counter eliminates lots of limitations which go far in Asynchronous counter.

The advantages of the Synchronous counter is as follows-

- Information technology'due south easier to design than the Asynchronous counter.

- It acts simultaneously.

- No propagation delay associated with it.

- Count sequence is controlled using logic gates, error chances are lower.

- Faster performance than the Asynchronous counter.

Although there are many advantages, one major disadvantage of working with Synchronous counter is that information technology requires a lot of extra logic to perform.

Use of Synchronous Counter

Few applications where Synchronous counters are used-

- Machine Motility control

- Motor RPM counter

- Rotary Shaft Encoders

- Digital clock or pulse generators.

- Digital Watch and Alert systems.

Source: https://circuitdigest.com/tutorial/synchronous-counter

0 Response to "How to Get Counter to Start at 0 Again"

Post a Comment